# *n*-type polysilicon by PVD enabling self-aligned back contact solar cells

Erik Hoffmann<sup>1</sup>, Philip Jäger<sup>2</sup>, Thorsten Dullweber<sup>2</sup>, Rolf Brendel<sup>2</sup>, Geoffrey Gregory<sup>1</sup>, Muhammad Khan<sup>1</sup>, Nabeel Khan<sup>1</sup>, Massimo Centazzo<sup>1</sup> <sup>1</sup>EnPV GmbH, Durlacher Allee, Karlsruhe, 76131, Germany

<sup>2</sup>Institute for Solar Energy Research Hamelin (ISFH), Am Ohrberg 1, 31860 Emmerthal, Germany

#### Introduction

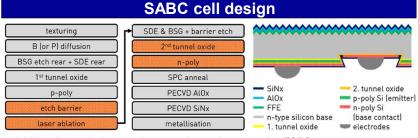

- Innovative IBC solar cell process with phosphorous doped *n*-type polysilicon by directional physical vapor deposition (PVD).

- Self aligned separation of the polysilicon contacts via shading from PVD at under-etched trenches.

- Can be integrated into an existing TOPCon manufacturing line with the addition of only two tools

- Investigation of *n*-type polysilicon and *n*-type/*p*-type polysilicon stack on planar and on laser patterned, structured surfaces.

- · Additionally required processing steps (orange) compared to TOPCon:

- etch barrier (EB) deposition

- · laser patterning of EB

- tunnel oxide (TO) deposition

- n-type polysilicon PVD

- Etching of trenches simultaneous to *p*-poly wrap around etch

- n-type polysilicon covers full rear side:

- except shaded trench edge  $\Rightarrow$  insulation of emitter and base contact

- n<sup>++</sup>/p<sup>++</sup>- tunneling junction at emitter

- only one metallization step required to contact the *n*-type polysilicon on both passivated contacts

Results

#### n-type polysilicon:

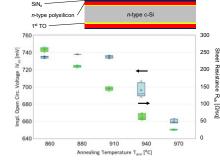

- symmetric TO, n-type polysilicon by PVD on n-type Cz wafers after annealing, passivation with SiN<sub>X</sub> and fast firing

- up to iV\_{oc} = 738 mV after annealing at  $T_{ann}$  = 880  $^{\circ}\mathrm{C}$

- decreasing sheet resistance R<sub>sh</sub> with increasing annealing temperature

- for optimum T<sub>ann</sub> = 880 °C, sheet resistance yields R<sub>sh</sub> = 208 Ω/sq ⇔ sufficiently low R<sub>sh</sub> for the base contact of an IBC solar cell

Implied open circuit voltage  $iV_{OC}$  and sheet resistance  $R_{sh}$  of symmetric *n*-type polysilicon.

#### *n*-type/p-type polysilicon layer stack:

- including 1<sup>st</sup> and 2<sup>nd</sup> TO

- symmetric stack on n-type Cz wafer, annealing,  $\text{SIN}_{\text{X}}$  deposition and fast firing

- up to iV\_{OC} = 715 mV after annealing at  $\rm T_{ann}$  = 870 °C

- *p*-type polysilicon layer alone yields higher iV<sub>oc</sub> = 726 mV, indicating lower passivation quality induced by the *n*-type layer

- low sheet resistance  $R_{sh} = 97 \Omega/sq$  due to the two conductive layers.  $R_{sh}$  in good agreement to calculated  $R_{sh,ca} = 94 \Omega/sq$ from  $R_{sh}$  of individual layers

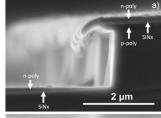

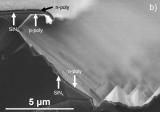

- SEM image of a trench cross-section after:

- a) isotropic and b) anisotropic wetchemical etching of *p*-type polysilicon and c-Si wafer surface

- · etch barrier removal and cleaning

- SiN<sub>x</sub> deposition (to enhance contrast between silicon layers)

- PVD of *n*-type polysilicon

- annealing

- Both etchants under-cut barrier layer and p-type polysilicon

- *n*-type polysilicon layer thickness (\$ 120 nm) thins as it approaches the trench wall and even disappears

$iV_{\text{OC}}$  and  $R_{\text{sh}}$  of symmetric p-type/n-type polysilicon including first and second TO.

SEM images of a) isotropic and b) anisotropic etched trenches. For both the thickness of the *n*-poly silicon layer reduces as it approaches the trench wall

### Conclusion

- High iV<sub>oc</sub> of base contact *n*-type polysilicon layer and promising iV<sub>oc</sub> of emitter *n*-type polysilicon/TO/*p*-type polysilicon stack.

- Optimum annealing temperature of both layers in the same range T<sub>ann</sub> = 870 880 °C, hence, enabling co-annealing.

- Low R<sub>sh</sub> of layer stack indicates low resistance across the interfacial TO between polysilicon layers and allows further optimization of doping concentration and thickness of each layer.

- Wet-chemical etching of *p*-type polysilicon and c-Si wafer surface after laser patterning of SiN<sub>x</sub> etch barrier under-cuts both etch barrier and *p*-type polysilicon.

- Under-cut shades subsequent PVD of *n*-type polysilicon at trench edge, hence separating the *n*-type polysilicon layer between base contact and emitter.

- Further proof of contact insulation and first proof of concept solar cells under development.

## • low s